| ID |

Date |

Author |

Project |

Subject |

Run Number |

Events |

StartTime |

EndTime |

Data |

|

23

|

Mon Oct 3 21:08:27 2011 |

Manfred Valentan | Micron | Micron-Baby-Stack p-stop, configuration | | | | | | Photo of hand-drawn stack configuration, config files |

| Attachment 1: Micron-Baby-Stack_p-stop.png

|  |

| Attachment 2: cern11_micronbaby_pstop_single.cfg

|

# 40 mhz

# single peak mode (1 sample)

# 50ns peaking time

# 30ns trigger window (built from 5ns window, thus ~12.5ns later)

# NECO

#

# Data processing with FADC+PROC

# FADC 0 = p-side ch 4-7 origami;

# FADC 1 = n-side ch 4-7 origami;

#

# CERN SPS testbeam 2011

# micron baby stack with p-stop sensors

#

# CI 3 Oct 2011

#

#

# Lines preceded by a # or ; sign are ignored.

#

# [rem] comments a whole section until the next section start marked by [xxx] .

#

# [vme]

# VME addresses are given in the format

# {module_name} = {vme_module_number},{vme_address_hex}

# nec ... NECO module

# adf ... particular FADC module

#

# Please note that the address ranges are not defined here,

# they are implicitly given by the hardware.

# Module numbers must fill from 0 (this is not checked).

# Please note that no range checking is performed.

# There is no access to VME modules that are not included in this list,

[vme]

nec = 0,0x1a000000

adf = 0,0x1b000000

adf = 1,0x2b000000

# [nec]

# NECO related information

# mod = 0|1,{shift_register_delay},{adc_range},{win_delay},{win_length},{dead_time},{time_lat},{max_trg}

# (default: 0,75,0,50?,900?,36,2,1)

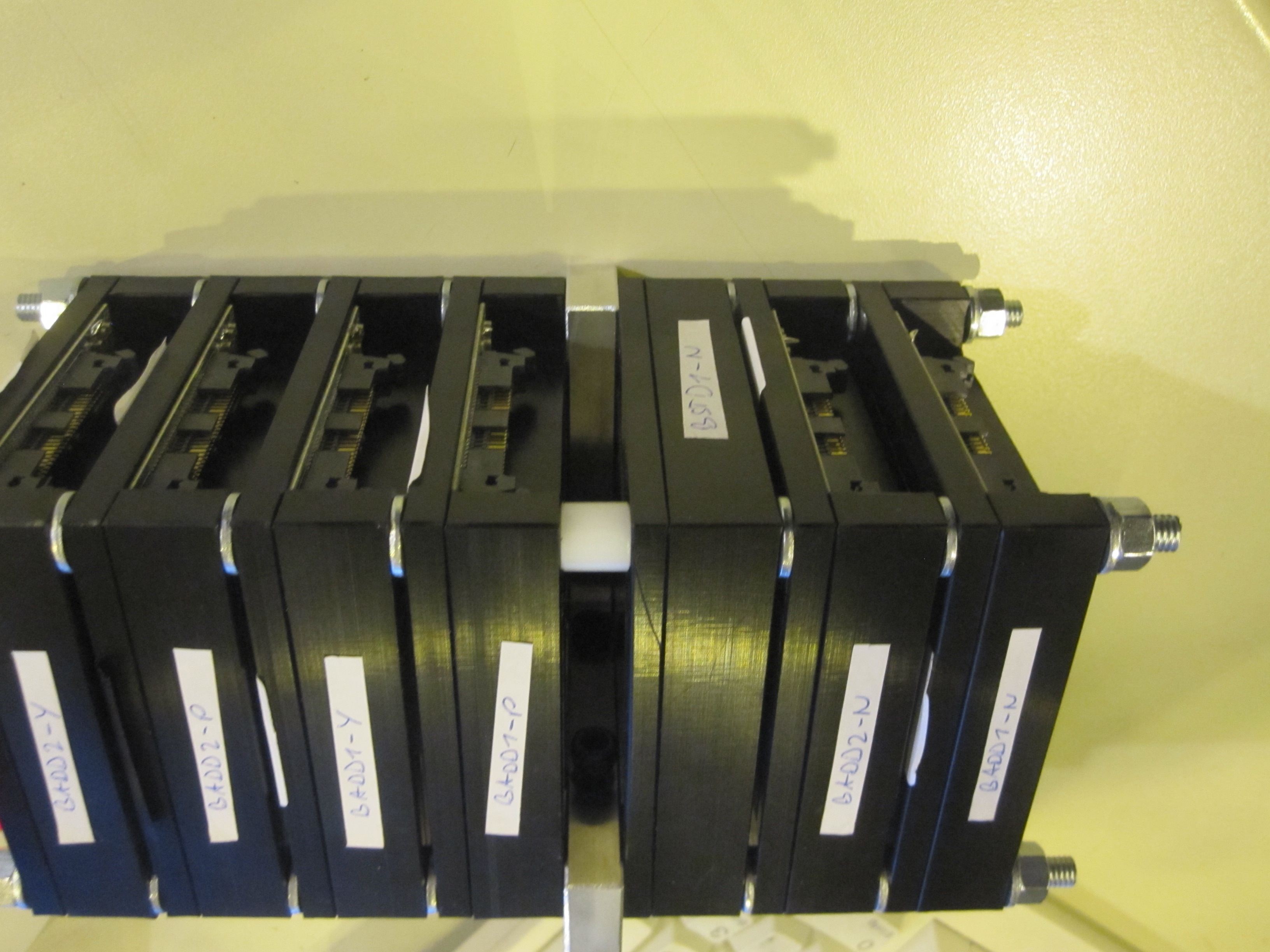

# res = {list of entries in reset sequence} (default: 2,4)

# cal = {list of entries in cal sequence} (default: 2,3,250,251)

# sw5 = {list of entries in single cal sequence} (default: 2,3)

# str = {list of entries in software trigger sequence} (default: 75)

# htr = {list of entries in hardware trigger sequence} (default: 74)

#

# mod specifies to use either the sequencer (0) or the shift register (1) for hardware trigger and the

# delay of the shift register (0..255); adc_range (0=1Vpp, 1=2Vpp) -- ignored; win_delay and win_length define

# the starting point (relative to the APV trigger) and length of the ADC gate in transparent mode; dead_time is

# the number of 254MHz clock cycles which are set to zero for time measurement after an incoming trigger;

# time_lat is the latency for time measurement in terms of 40MHz clock cycles; max_trg is the number of incoming

# triggers which required to activate the veto logic (usually 1; 0 completely disables the veto logic)

# res, cal, sw5, str and htr are containing the bits to set in the 256-element sequencer memory (nothing is set at -1)

# Please note that cal+str together produce a calibration request plus subsequent normal trigger, so the time

# between them is the latency. sw5 is used to send a single cal request to achieve the correct polarity in

# case the APV inverter is turned on (this feature only works for entire MAMBOs halves = groups of 3 REBOs)

#

# These settings are quite fragile! Do not modify until you know exactly what you are doing.

[nec]

# 30m cables, 40mhz, Tp=50ns, single-trigger

mod = 0,75,0,70,250,36,2,1

htr = 63,-1,-1,-1,-1,-1,-1,-1

str = 100,-1,-1,-1,-1,-1,-1,-1

# TESTBEAM May 08, 30m cables, 40mhz, Tp=50ns, multi-trigger (6 samples)

#mod = 0,75,0,70,950,36,2,1

#htr = 61,64,-1,-1,-1,-1,-1,-1

#str = 100,103,-1,-1,-1,-1,-1,-1

#common settings

res = 2, 4, -1, -1,-1,-1,-1,-1

cal = 2, 3,250,251,-1,-1,-1,-1

sw5 = 2, 3, -1, -1,-1,-1,-1,-1

# [daq]

# DAQ related specifications are given in the format

# ads = {N},{search_max_subevents},0,x

# ini = {initevents},{readout_mode},0,x

# deh = {module_position},{apv_position},0,x

# i2t = {N},0,0,x

# pat = 0,0,0,{data_file_path}

# clk = {N},{Delay25 frequency range},0,x

# pdl = {Trigger input delay},0,0,x

# crd = {crate_number},{clkdel},{trgdel},x

#

# ads N gives the number of samples that are read out from the FIFO1 in transparent mode, search_max_subevents is the

# maximum number of subevents to search for within one ADC stream (default=1).

# ini: initevents is the number of software triggers in the beginning of a run for pedestal and noise

# evaluation. At the beginning of each run, 2*initevents are generated by software, after that the

# selected trigger source (hardware, software of calibration) is activated. The initial evaluation

# events are written to disk as normal events are.

# ini: readout_mode defines whether events beyond the initevents are read in raw transparent mode from FIFO1 (0) or

# in processed mode (1) where only hit information is read from FIFO3

# deh is the APV chip for which single strip histograms are recorded

# i2t is the maximum number of I2C retries in case of failure

# pat specifies the save path for data files (must include a trailing backslash!)

# clk gives the system clock period in integer ns (25 max.) and the frequency range for the Delay25 chip:

# 0...40 MHz, 1...80 MHz, 2...32 MHz, 3...64 MHz

# pdl specifies the delay setting for the trigger input in 0.5ns steps (0..49)

# crd define the global clock and trigger delays between NECO and SVD3_buffer for crates 0 and 1

# NOTE: clock and trigger is NOT propagated to any crate(s) NOT specified here

[daq]

# TESTBEAM May 08

#Standard

ads = 250,1,0,x

# TESTBEAM May 08

#Multitrigger (6)

#ads = 950,6,0,x

# RAW (transparent mode) readout

ini = 300,0,0,x

# PROCESSED readout

#ini = 300,1,0,x

deh = 1,0,0,x

i2t = 5,0,0,x

pat = 0,0,0,D:\cern11\micronbaby\data

#standard 40mhz clock (25ns)

clk = 25,0,0,x

pdl = 25,0,0,x

#crate distribution delays (set to mid-range to allow adjustments in both directions)

crd = 0,25,25,x

#we don't use crate 1, so we don't set any delay here -> no clock/trigger to crate 1

###crd = 1,25,25,x

# [hit]

# Hit recognition variables are specified here

# hcs = {hitcut_seed_strip},{hitcut_neighbor_strips}

# nok = {x.x},0

#

#

# hcs gives seed and neighbor hit cuts in units of strip sigma

# nok states the threshold over average noise at which strips are excluded from further analysis (to exclude noisy strips)

[hit]

# si sensor

hcs = 4.0,4.0

# do not exclude strips

nok = 2000.0,0

# [cal]

# Calibration related data

# lvl = {level},0

# lat = {latbeg},{latend}

# sam = {average_samples},{number of samples in 6-tuple mode}

# grp = {number_of_groups},0

# lg6 = {latency},{group}

# lv6 = {startlevel},{endlevel}

#

# lvl is the CLVL amplitude (0..255), 1 is 625e-, 36 is 1 MIP (22500e-) nominally, in reality 26 is 1 MIP

# lat is the Latency range to cover (latend-latbeg>=2, latend-latbeg<=15)

# sam is the number of samples to average per position for normal and 6-tuple modes

# grp is how many groups to scan (<=8), first group is strips 0,8,16,..., second group is 1,9,17,..., ...

# lg6 defines the latency in 6-tuple mode and which group to observe in that mode

# lv6 defines the scan range of amplitude in 6-tuple mode

[cal]

#real 1 MIP level (22400e)

lvl = 26,0

#real 5 MIPs level

#lvl = 130,0

#LAT=95/98 Calibration (short display)

#lat = 89,100

#LAT=95/98 Calibration (short display for >=50mhz)

#lat = 81,98

#LAT=95/98 Calibration (long peak mode tail display)

lat = 75,100

#common settings

sam = 50,500

grp = 8,0

#6-tuple mode settings

lg6 = 97, 1

lv6 = 1,200

# [i2c]

# This section defines one or more I2C sets for the APV25. In the [mod] section, those sets are referenced to by their number.

# ia2 = {number},{mode},{lat},{ipre},{ipcasc},{ipsf},{isha},{issf},{ipsp},{imuxin},{vfp},{vfs},{vpsp},{muxgain}

#

# The I2C settings must be individually numbered (ascending from 0). The easiest case is to use the same

# settings for all chips of one type, but one could go so far to use separate settings for each chip.

# vadj/vpsp is set individually for each apv in the [mod] section, the value specified here is meaningless.

[i2c]

# apv25s1, peak, inverter ON, Tp=50ns, (p side)

ia2 = 0, 63, 95, 98, 52, 34, 34, 34, 55, 34, 30, 60, 0, 4

# apv25s1, peak, inverter OFF, Tp=50ns, (n side)

ia2 = 1, 31, 95, 98, 52, 34, 34, 34, 55, 34, 30, 60, 0, 4

# apv25s1, multi-peak, inverter ON, Tp=50ns, (p side)

#ia2 = 0, 61, 95, 98, 52, 34, 34, 34, 55, 34, 30, 60, 0, 4

# apv25s1, multi-peak, inverter OFF, Tp=50ns, (n side)

#ia2 = 1, 29, 95, 98, 52, 34, 34, 34, 55, 34, 30, 60, 0, 4

# [mod]

# Detector module (actually hybrid) specifications are given in the format

# mod = {module_position},{crate_number},{mambo_number},{rebo_number},{hybrid_number},m,{AD8128_peak},{rebo_clkdelay},{rebo_trgdelay},0,0,0,0,{Name}

# apv = {module_position},{apv_position},{i2c_address},{i2c_settings},{vadj/vpsp},x,0,0,{fadc_offset},{fadc_number},{fadc_channel},{fadc_clkdelay [0..49]},{AD8128_gain},x

#

# mod gives the hybrid/module properties: The position counts from 0 to 7 in beam direction,

# Name must not contain blanks ("_" is allowed).

# apv describes the chips located on a hybrid

# and the ADC channel where they are read out, either a Vienna ADC (a) or a FED (f).

# The ADC offset is only available with the Vienna ADCs and shifts the baseline.

# The individual chip vadj setting dominates over the [i2c] setting.

[mod]

# mambo 0

mod = 0,0,0,2,0,m,45,25,0,0,0,0,0, atoll-2

apv = 0,0,38,1,30,x,0,0,5,0,2,22,100,x

apv = 0,1,40,1,30,x,0,0,5,0,3,16,100,x

mod = 1,0,0,2,1,m,45,25,0,0,0,0,0, comb-2

apv = 1,0,38,1,30,x,0,0,5,0,6,26,100,x

apv = 1,1,40,1,30,x,0,0,5,0,7,22,100,x

mod = 2,0,0,2,2,m,45,25,0,0,0,0,0, comm-2

apv = 2,0,38,1,30,x,0,0,5,0,10,25,100,x

apv = 2,1,40,1,30,x,0,0,5,0,11,25,100,x

mod = 3,0,0,2,3,m,45,25,0,0,0,0,0, atoll-1

apv = 3,0,38,1,30,x,0,0,5,0,14,25,100,x

apv = 3,1,40,1,30,x,0,0,5,0,15,20,100,x

# mambo 1

mod = 4,0,1,1,0,m,45,25,0,0,0,0,0, comb-1

apv = 4,0,38,1,30,x,0,0,120,1,2,22,100,x

apv = 4,1,40,1,30,x,0,0,120,1,3,20,100,x

mod = 5,0,1,1,1,m,45,25,0,0,0,0,0, comm-1

apv = 5,0,38,1,30,x,0,0,120,1,6,22,100,x

apv = 5,1,40,1,30,x,0,0,120,1,7,18,100,x

# [bad]

# Bad channels description table

# bad = {module_position},{apv_position},{List of 18 strip values or -1}

#

# Maps bad channels, which are then excluded from hit search. Up to 18 bad strips can be entered per line,

# more lines per APV are allowed. Unused values in the list must be filled with -1

[bad]

#### atoll-2 ####

# every second channel is removed at sensor side --> noisy --> bad

bad = 0,0,0, 2, 4, 6, 8, 10, 12, 14, 16, 18, 20,22,24,26,28, 30, 32, 34

bad = 0,0,36, 38, 40, 42, 44, 46, 48, 50, 52, 54, 56,58,60,62,64, 66, 68, 70

bad = 0,0,72, 74, 76, 78, 80, 82, 84, 86, 88, 90, 92,94,96,98,100,102,104,106

bad = 0,0,108,110,112,114,116,118,120,122,124,126,-1,-1,-1,-1,-1, -1, -1, -1

bad = 0,1,0, 2, 4, 6, 8, 10, 12, 14, 16, 18, 20,22,24,26,28, 30, 32, 34

bad = 0,1,36, 38, 40, 42, 44, 46, 48, 50, 52, 54, 56,58,60,62,64, 66, 68, 70

bad = 0,1,72, 74, 76, 78, 80, 82, 84, 86, 88, 90, 92,94,96,98,100,102,104,106

bad = 0,1,108,110,112,114,116,118,120,122,124,126,-1,-1,-1,-1,-1, -1, -1, -1

#### comb-2 ####

# every second channel is removed at sensor side --> noisy --> bad

bad = 1,0,0, 2, 4, 6, 8, 10, 12, 14, 16, 18, 20,22,24,26,28, 30, 32, 34

bad = 1,0,36, 38, 40, 42, 44, 46, 48, 50, 52, 54, 56,58,60,62,64, 66, 68, 70

bad = 1,0,72, 74, 76, 78, 80, 82, 84, 86, 88, 90, 92,94,96,98,100,102,104,106

bad = 1,0,108,110,112,114,116,118,120,122,124,126,-1,-1,-1,-1,-1, -1, -1, -1

bad = 1,1,0, 2, 4, 6, 8, 10, 12, 14, 16, 18, 20,22,24,26,28, 30, 32, 34

bad = 1,1,36, 38, 40, 42, 44, 46, 48, 50, 52, 54, 56,58,60,62,64, 66, 68, 70

bad = 1,1,72, 74, 76, 78, 80, 82, 84, 86, 88, 90, 92,94,96,98,100,102,104,106

bad = 1,1,108,110,112,114,116,118,120,122,124,126,-1,-1,-1,-1,-1, -1, -1, -1

#### comm-2 ####

# every second channel is removed at sensor side --> noisy --> bad

bad = 2,0,0, 2, 4, 6, 8, 10, 12, 14, 16, 18, 20,22,24,26,28, 30, 32, 34

... 104 more lines ...

|

| Attachment 3: cern11_micronbaby_pstop_multi6.cfg

|

# 40 mhz

# multi peak mode (6 samples)

# 50ns peaking time

# 30ns trigger window (built from 5ns window, thus ~12.5ns later)

# NECO

#

# Data processing with FADC+PROC

# FADC 0 = p-side ch 4-7 origami;

# FADC 1 = n-side ch 4-7 origami;

#

# CERN SPS testbeam 2011

# micron baby stack with p-stop sensors

#

# CI 3 Oct 2011

#

#

# Lines preceded by a # or ; sign are ignored.

#

# [rem] comments a whole section until the next section start marked by [xxx] .

#

# [vme]

# VME addresses are given in the format

# {module_name} = {vme_module_number},{vme_address_hex}

# nec ... NECO module

# adf ... particular FADC module

#

# Please note that the address ranges are not defined here,

# they are implicitly given by the hardware.

# Module numbers must fill from 0 (this is not checked).

# Please note that no range checking is performed.

# There is no access to VME modules that are not included in this list,

[vme]

nec = 0,0x1a000000

adf = 0,0x1b000000

adf = 1,0x2b000000

# [nec]

# NECO related information

# mod = 0|1,{shift_register_delay},{adc_range},{win_delay},{win_length},{dead_time},{time_lat},{max_trg}

# (default: 0,75,0,50?,900?,36,2,1)

# res = {list of entries in reset sequence} (default: 2,4)

# cal = {list of entries in cal sequence} (default: 2,3,250,251)

# sw5 = {list of entries in single cal sequence} (default: 2,3)

# str = {list of entries in software trigger sequence} (default: 75)

# htr = {list of entries in hardware trigger sequence} (default: 74)

#

# mod specifies to use either the sequencer (0) or the shift register (1) for hardware trigger and the

# delay of the shift register (0..255); adc_range (0=1Vpp, 1=2Vpp) -- ignored; win_delay and win_length define

# the starting point (relative to the APV trigger) and length of the ADC gate in transparent mode; dead_time is

# the number of 254MHz clock cycles which are set to zero for time measurement after an incoming trigger;

# time_lat is the latency for time measurement in terms of 40MHz clock cycles; max_trg is the number of incoming

# triggers which required to activate the veto logic (usually 1; 0 completely disables the veto logic)

# res, cal, sw5, str and htr are containing the bits to set in the 256-element sequencer memory (nothing is set at -1)

# Please note that cal+str together produce a calibration request plus subsequent normal trigger, so the time

# between them is the latency. sw5 is used to send a single cal request to achieve the correct polarity in

# case the APV inverter is turned on (this feature only works for entire MAMBOs halves = groups of 3 REBOs)

#

# These settings are quite fragile! Do not modify until you know exactly what you are doing.

[nec]

# 30m cables, 40mhz, Tp=50ns, single-trigger

#mod = 0,75,0,70,250,36,2,1

#htr = 63,-1,-1,-1,-1,-1,-1,-1

#str = 100,-1,-1,-1,-1,-1,-1,-1

# TESTBEAM May 08, 30m cables, 40mhz, Tp=50ns, multi-trigger (6 samples)

mod = 0,75,0,70,950,36,2,1

htr = 58,61,-1,-1,-1,-1,-1,-1

str = 100,103,-1,-1,-1,-1,-1,-1

#common settings

res = 2, 4, -1, -1,-1,-1,-1,-1

cal = 2, 3,250,251,-1,-1,-1,-1

sw5 = 2, 3, -1, -1,-1,-1,-1,-1

# [daq]

# DAQ related specifications are given in the format

# ads = {N},{search_max_subevents},0,x

# ini = {initevents},{readout_mode},0,x

# deh = {module_position},{apv_position},0,x

# i2t = {N},0,0,x

# pat = 0,0,0,{data_file_path}

# clk = {N},{Delay25 frequency range},0,x

# pdl = {Trigger input delay},0,0,x

# crd = {crate_number},{clkdel},{trgdel},x

#

# ads N gives the number of samples that are read out from the FIFO1 in transparent mode, search_max_subevents is the

# maximum number of subevents to search for within one ADC stream (default=1).

# ini: initevents is the number of software triggers in the beginning of a run for pedestal and noise

# evaluation. At the beginning of each run, 2*initevents are generated by software, after that the

# selected trigger source (hardware, software of calibration) is activated. The initial evaluation

# events are written to disk as normal events are.

# ini: readout_mode defines whether events beyond the initevents are read in raw transparent mode from FIFO1 (0) or

# in processed mode (1) where only hit information is read from FIFO3

# deh is the APV chip for which single strip histograms are recorded

# i2t is the maximum number of I2C retries in case of failure

# pat specifies the save path for data files (must include a trailing backslash!)

# clk gives the system clock period in integer ns (25 max.) and the frequency range for the Delay25 chip:

# 0...40 MHz, 1...80 MHz, 2...32 MHz, 3...64 MHz

# pdl specifies the delay setting for the trigger input in 0.5ns steps (0..49)

# crd define the global clock and trigger delays between NECO and SVD3_buffer for crates 0 and 1

# NOTE: clock and trigger is NOT propagated to any crate(s) NOT specified here

[daq]

# TESTBEAM May 08

#Standard

#ads = 250,1,0,x

# TESTBEAM May 08

#Multitrigger (6)

ads = 950,6,0,x

# RAW (transparent mode) readout

ini = 300,0,0,x

# PROCESSED readout

#ini = 300,1,0,x

deh = 1,0,0,x

i2t = 5,0,0,x

pat = 0,0,0,D:\cern11\micronbaby\data

#standard 40mhz clock (25ns)

clk = 25,0,0,x

pdl = 25,0,0,x

#crate distribution delays (set to mid-range to allow adjustments in both directions)

crd = 0,25,25,x

#we don't use crate 1, so we don't set any delay here -> no clock/trigger to crate 1

###crd = 1,25,25,x

# [hit]

# Hit recognition variables are specified here

# hcs = {hitcut_seed_strip},{hitcut_neighbor_strips}

# nok = {x.x},0

#

#

# hcs gives seed and neighbor hit cuts in units of strip sigma

# nok states the threshold over average noise at which strips are excluded from further analysis (to exclude noisy strips)

[hit]

# si sensor

hcs = 4.0,4.0

# do not exclude strips

nok = 2000.0,0

# [cal]

# Calibration related data

# lvl = {level},0

# lat = {latbeg},{latend}

# sam = {average_samples},{number of samples in 6-tuple mode}

# grp = {number_of_groups},0

# lg6 = {latency},{group}

# lv6 = {startlevel},{endlevel}

#

# lvl is the CLVL amplitude (0..255), 1 is 625e-, 36 is 1 MIP (22500e-) nominally, in reality 26 is 1 MIP

# lat is the Latency range to cover (latend-latbeg>=2, latend-latbeg<=15)

# sam is the number of samples to average per position for normal and 6-tuple modes

# grp is how many groups to scan (<=8), first group is strips 0,8,16,..., second group is 1,9,17,..., ...

# lg6 defines the latency in 6-tuple mode and which group to observe in that mode

# lv6 defines the scan range of amplitude in 6-tuple mode

[cal]

#real 1 MIP level (22400e)

lvl = 26,0

#real 5 MIPs level

#lvl = 130,0

#LAT=95/98 Calibration (short display)

#lat = 89,100

#LAT=95/98 Calibration (short display for >=50mhz)

#lat = 81,98

#LAT=95/98 Calibration (long peak mode tail display)

lat = 75,100

#common settings

sam = 50,500

grp = 8,0

#6-tuple mode settings

lg6 = 97, 1

lv6 = 1,200

# [i2c]

# This section defines one or more I2C sets for the APV25. In the [mod] section, those sets are referenced to by their number.

# ia2 = {number},{mode},{lat},{ipre},{ipcasc},{ipsf},{isha},{issf},{ipsp},{imuxin},{vfp},{vfs},{vpsp},{muxgain}

#

# The I2C settings must be individually numbered (ascending from 0). The easiest case is to use the same

# settings for all chips of one type, but one could go so far to use separate settings for each chip.

# vadj/vpsp is set individually for each apv in the [mod] section, the value specified here is meaningless.

[i2c]

# apv25s1, peak, inverter ON, Tp=50ns, (p side)

#ia2 = 0, 63, 95, 98, 52, 34, 34, 34, 55, 34, 30, 60, 0, 4

# apv25s1, peak, inverter OFF, Tp=50ns, (n side)

#ia2 = 1, 31, 95, 98, 52, 34, 34, 34, 55, 34, 30, 60, 0, 4

# apv25s1, multi-peak, inverter ON, Tp=50ns, (p side)

ia2 = 0, 61, 95, 98, 52, 34, 34, 34, 55, 34, 30, 60, 0, 4

# apv25s1, multi-peak, inverter OFF, Tp=50ns, (n side)

ia2 = 1, 29, 95, 98, 52, 34, 34, 34, 55, 34, 30, 60, 0, 4

# [mod]

# Detector module (actually hybrid) specifications are given in the format

# mod = {module_position},{crate_number},{mambo_number},{rebo_number},{hybrid_number},m,{AD8128_peak},{rebo_clkdelay},{rebo_trgdelay},0,0,0,0,{Name}

# apv = {module_position},{apv_position},{i2c_address},{i2c_settings},{vadj/vpsp},x,0,0,{fadc_offset},{fadc_number},{fadc_channel},{fadc_clkdelay [0..49]},{AD8128_gain},x

#

# mod gives the hybrid/module properties: The position counts from 0 to 7 in beam direction,

# Name must not contain blanks ("_" is allowed).

# apv describes the chips located on a hybrid

# and the ADC channel where they are read out, either a Vienna ADC (a) or a FED (f).

# The ADC offset is only available with the Vienna ADCs and shifts the baseline.

# The individual chip vadj setting dominates over the [i2c] setting.

[mod]

# mambo 0

mod = 0,0,0,2,0,m,45,25,0,0,0,0,0, atoll-2

apv = 0,0,38,1,30,x,0,0,5,0,2,22,100,x

apv = 0,1,40,1,30,x,0,0,5,0,3,16,100,x

mod = 1,0,0,2,1,m,45,25,0,0,0,0,0, comb-2

apv = 1,0,38,1,30,x,0,0,5,0,6,26,100,x

apv = 1,1,40,1,30,x,0,0,5,0,7,22,100,x

mod = 2,0,0,2,2,m,45,25,0,0,0,0,0, comm-2

apv = 2,0,38,1,30,x,0,0,5,0,10,25,100,x

apv = 2,1,40,1,30,x,0,0,5,0,11,25,100,x

mod = 3,0,0,2,3,m,45,25,0,0,0,0,0, atoll-1

apv = 3,0,38,1,30,x,0,0,5,0,14,25,100,x

apv = 3,1,40,1,30,x,0,0,5,0,15,20,100,x

# mambo 1

mod = 4,0,1,1,0,m,45,25,0,0,0,0,0, comb-1

apv = 4,0,38,1,30,x,0,0,120,1,2,22,100,x

apv = 4,1,40,1,30,x,0,0,120,1,3,20,100,x

mod = 5,0,1,1,1,m,45,25,0,0,0,0,0, comm-1

apv = 5,0,38,1,30,x,0,0,120,1,6,22,100,x

apv = 5,1,40,1,30,x,0,0,120,1,7,18,100,x

# [bad]

# Bad channels description table

# bad = {module_position},{apv_position},{List of 18 strip values or -1}

#

# Maps bad channels, which are then excluded from hit search. Up to 18 bad strips can be entered per line,

# more lines per APV are allowed. Unused values in the list must be filled with -1

[bad]

#### atoll-2 ####

# every second channel is removed at sensor side --> noisy --> bad

bad = 0,0,0, 2, 4, 6, 8, 10, 12, 14, 16, 18, 20,22,24,26,28, 30, 32, 34

bad = 0,0,36, 38, 40, 42, 44, 46, 48, 50, 52, 54, 56,58,60,62,64, 66, 68, 70

bad = 0,0,72, 74, 76, 78, 80, 82, 84, 86, 88, 90, 92,94,96,98,100,102,104,106

bad = 0,0,108,110,112,114,116,118,120,122,124,126,-1,-1,-1,-1,-1, -1, -1, -1

bad = 0,1,0, 2, 4, 6, 8, 10, 12, 14, 16, 18, 20,22,24,26,28, 30, 32, 34

bad = 0,1,36, 38, 40, 42, 44, 46, 48, 50, 52, 54, 56,58,60,62,64, 66, 68, 70

bad = 0,1,72, 74, 76, 78, 80, 82, 84, 86, 88, 90, 92,94,96,98,100,102,104,106

bad = 0,1,108,110,112,114,116,118,120,122,124,126,-1,-1,-1,-1,-1, -1, -1, -1

#### comb-2 ####

# every second channel is removed at sensor side --> noisy --> bad

bad = 1,0,0, 2, 4, 6, 8, 10, 12, 14, 16, 18, 20,22,24,26,28, 30, 32, 34

bad = 1,0,36, 38, 40, 42, 44, 46, 48, 50, 52, 54, 56,58,60,62,64, 66, 68, 70

bad = 1,0,72, 74, 76, 78, 80, 82, 84, 86, 88, 90, 92,94,96,98,100,102,104,106

bad = 1,0,108,110,112,114,116,118,120,122,124,126,-1,-1,-1,-1,-1, -1, -1, -1

bad = 1,1,0, 2, 4, 6, 8, 10, 12, 14, 16, 18, 20,22,24,26,28, 30, 32, 34

bad = 1,1,36, 38, 40, 42, 44, 46, 48, 50, 52, 54, 56,58,60,62,64, 66, 68, 70

bad = 1,1,72, 74, 76, 78, 80, 82, 84, 86, 88, 90, 92,94,96,98,100,102,104,106

bad = 1,1,108,110,112,114,116,118,120,122,124,126,-1,-1,-1,-1,-1, -1, -1, -1

#### comm-2 ####

# every second channel is removed at sensor side --> noisy --> bad

bad = 2,0,0, 2, 4, 6, 8, 10, 12, 14, 16, 18, 20,22,24,26,28, 30, 32, 34

... 104 more lines ...

|

|

24

|

Tue Oct 4 00:11:31 2011 |

Manfred Valentan | Micron | Micron-Baby-Stack p-stop, zones w & h-w | run002 | 760000 | 04.10.2011 00:11:06 | 04.10.2011 09:01:06 | Good | hit modules in bottom left corner -> Zones wide and half-wide for all modules

Position of HEPHY x-z-table:

x = 336

z = 89 |

|

25

|

Tue Oct 4 10:44:09 2011 |

Christian Irmler | Micron | Internal Calibration | cal002 | 83800 | 04.10.2011 10:04:49 | 04.10.2011 10:19:41 | | micronbaby p-spray/irrad

HV = -100V

beam on,

irrad APVs with standard baseline settings --> too high

APV #2 (I²C addr. 40) deactivated, latency error after initialization, reset line open? |

|

26

|

Tue Oct 4 10:44:48 2011 |

Christian Irmler | Micron | Internal Calibration | cal003 | 83800 | 04.10.2011 10:33:50 | 04.10.2011 10:48:51 | | micronbaby p-spray/irrad

HV = -100V

beam on, baseline of irrad APV reduced

APV #2 (I²C addr. 40) deactivated, latency error after initialization, reset line open? |

|

27

|

Tue Oct 4 10:47:59 2011 |

Manfred Valentan | Micron | Internal Calibration | cal001 | 83800 | 03.10.2011 20:34:48 | 03.10.2011 20:50:57 | | micronbaby p-stop stack

HV = -100V

beam on |

|

28

|

Tue Oct 4 15:16:06 2011 |

Manfred Valentan | Micron | Micron-Baby-Stack p-spray, run bottom left | run003 | 200k | 04.10.2011 11:29:19 | 04.10.2011 13:57:54 | Good | hit modules in bottom left corner -> Zones wide and half-wide for COMB_IRRAD, Zones narrow and half-narrow for BOMM_IRRAD

Position of HEPHY x-z-table:

x = 336

z = 89 |

|

29

|

Tue Oct 4 15:16:45 2011 |

Manfred Valentan | Micron | Micron-Baby-Stack p-spray, run bottom right NOT USABLE | run004 | 200k | 4.10.2011 15:28:48 | 04.10.2011 19:36:50 | Crap | HAS TO BE REPEATED!!! Before this run there were changes in the trigger line (vetoing the trigger when no spill), and thus the timing is incorrect.

hit modules in bottom right corner -> Zones narrow and half-narrow for COMB_IRRAD, Zones wide and half-wide for COMM_IRRAD

Position of HEPHY x-z-table:

x = 322

z = 89 |

|

68

|

Mon Oct 10 21:54:24 2011 |

Marko Dragicevic | Micron | Micron-Baby-Stack p-spray, run bottom right | run027 | 700k | 10.10.2011 22:40:31 | 11.10.2011 09:49:11 | Unknown | hit modules in bottom left corner -> Zones narrow and half-narrow for COMB_IRRAD, Zones wide and half-wide for COMM_IRRAD

timing corrected w.r.t. run004

Position of HEPHY x-z-table:

x = 322

z = 70

Note: z-Position not identical with position of run004, x-z-table seemed to have moved vertically. This configuration now hits the same sensor position. |

|

69

|

Mon Oct 10 21:55:30 2011 |

Marko Dragicevic | Micron | Internal Calibration | cal013 | 83800 | 10.10.2011 21:52:32 | | Unknown | micronbaby p-spray/irrad

HV = -100V

beam on, baseline of irrad APV reduced

APV #2 (I²C addr. 40) deactivated, latency error after initialization, reset line is open |

|

50

|

Sat Oct 8 14:33:25 2011 |

Thomas Bergauer | HPK | baby_std | run016 | 250k | 08.10.2011 14:31:40 | | Crap | falsches config file (single statt multi6)

no cooling

beam on; xy table position x=322 y=80

HV=200V Istart_PY=7.6uA; Istart_N=0.42

std. I2C settings |

|

51

|

Sat Oct 8 16:35:04 2011 |

Thomas Bergauer | HPK | baby_std | run017 | | 08.10.2011 16:26:10 | | Crap | wrong timing

no cooling

beam on; xy table position x=322 y=80

HV=200V Istart_PY=7.6uA; Istart_N=0.42

std. I2C settings |

|

52

|

Sat Oct 8 16:45:14 2011 |

Thomas Bergauer | HPK | baby_std | run018 | 150000 | 08.10.2011 16:44:13 | 08.10.2011 19:33:33 | Good | no cooling

beam on; xy table position x=322 y=80

HV=200V Istart_PY=8.2uA; Istart_N=0.45uA

std. I2C settings, now with correct timing |

|

53

|

Sat Oct 8 20:33:58 2011 |

Karl-Heinz Hoffmann | HPK | baby_std | run019 | 150000 | 08.10.2011 20:22:45 | 08.10.2011 23:19:23 | Good | no cooling

beam on; xy table position x=333 y=80

HV=200V Istart_PY=8.2uA; Istart_N=0.45uA

std. I2C settings |

|

54

|

Sat Oct 8 23:27:44 2011 |

Karl-Heinz Hoffmann | HPK | baby_std | run020 | 382000 | 08.10.2011 23:24:16 | 09.10.2011 09:24:20 | Good | no cooling

beam on; xy table position x=327,5 y=65

HV=200V Istart_PY=8.2uA; Istart_N=0.45uA

std. I2C settings |

|

55

|

Sun Oct 9 10:05:34 2011 |

Markus Friedl | HPK | baby_std | cal010 | 83800 | 08.10.2011 13:36:25 | 08.10.2011 13:54:07 | Good | HV=+-40V,

no cooling

beam off; xy table position x= y=

HV= Istart=uA;

std. I2C settings

|

|

56

|

Sun Oct 9 10:13:11 2011 |

Karl-Heinz Hoffmann | HPK | baby_add | cal011 | 83800 | 09.10.2011 10:05:01 | | Good | no cooling

beam on; xy table position x= y=

HV=200V Istart_P=1.5uA; Istart_N=0.22uA

std. I2C settings |

|

57

|

Sun Oct 9 11:00:33 2011 |

Karl-Heinz Hoffmann | HPK | baby_add | run021 | 150000 | 09.10.2011 10:56:47 | 09.10.2011 12:47:23 | Good | no cooling

beam on; xy table position x=330 y=74

HV=200V Istart_PY=1,9uA; Istart_N=0.27uA

std. I2C settings |

|

58

|

Sun Oct 9 11:28:30 2011 |

Manfred Valentan | HPK | HPK BSTD stack configuration | | | | | Unknown | Module order:

BSTD1-N

BSTD2-N

BADD1-N (for z information)

BSTD1-P

BSTD1-Y

BSTD2-P

BSTD2-Y

Talk from Marko on Testbeam with HPK Double Metal Sensors |

| Attachment 1: IMG_5058.JPG

|  |

| Attachment 2: IMG_5069.JPG

|  |

|

59

|

Sun Oct 9 11:31:43 2011 |

Manfred Valentan | HPK | HPK BADD stack configuration | | | | | Unknown | Module order:

BADD1-N

BADD2-N

BSTD1-N (for z information)

BADD1-P

BADD1-Y

BADD2-P

BADD2-Y

Talk from Marko on Testbeam with HPK Double Metal Sensors |

| Attachment 1: IMG_5097.JPG

|  |

|

60

|

Sun Oct 9 13:12:32 2011 |

Karl-Heinz Hoffmann | HPK | baby_add | run022 | 670k | 09.10.2011 13:09:32 | 10.10.2011 00:48:16 | Good | no cooling

beam on; xy table position x=330 y=64

HV=200V Istart_PY=1,9uA; Istart_N=0.27uA

std. I2C settings |

|