Internal calibration for "stealth parasitic" mode Belle stack; taken without beam

Belle Stack 4: 2 DSSD -z, Origami #3, #1, wedge new #2

HV = +-50V, Ibias=80A

Position: approx. centered

no beam

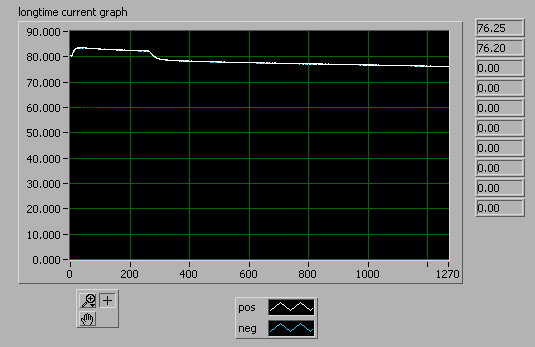

Total bias current history:

At the beginning, the system was already running for a few hours and the APV25 chips were initialized before, so thermal equilibrium was reached.

The actual calibration run happened during the first ~250 measurement points (~1 hour). It seems like the APVs draw a bit more current during internal calibration. The overall decay is supposedly due to a temperature decrease towards night.

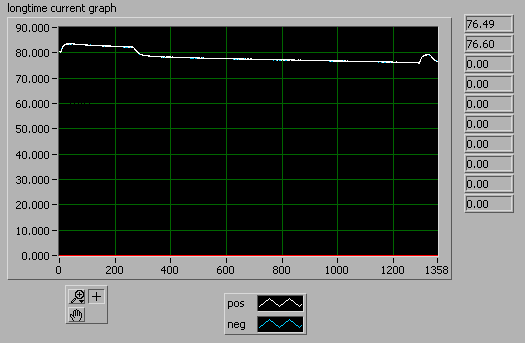

Now tried the same thing with a short software run - same effect:

Need to investigate supply currents while data taking - they should actually go up a bit - and their dependency on the trigger rate.

|